可编程ADC的实现

认知无线电接收机对其前端采用的高性能模-数转换器(ADC)及模拟器件的要求都较高,而FPGA在基带数字信号处理方面又迫切需要动态可重配置。为了适应以上要求,可以首先考虑使用可编程模拟器件来实现ADC,以下是两种具体实现方法。

FIPSOC混合信号片上系统

SIDSA公司的FIPSOC混合信号片上系统是快速开发模拟、数字集成应用的理想工具。FIPSOC芯片包括内嵌的增强型8051微处理器、现场可编程门阵列(FPGA)以及一组面向信号调理和数据采集应用的可灵活配置的模拟单元。与分离的模拟、数字FPGA方案相比,采用FIPSOC混合信号片上系统,可使产品设计周期缩短30~40%。

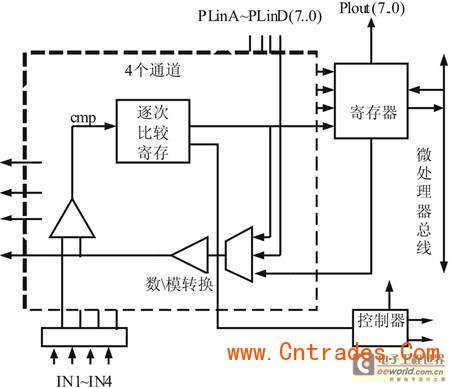

可编程的模拟、数字单元与8051的单片系统包括模拟单元、转换单元、可编程数字单元、8051内核和该系列中的所有器件具有兼容的存储器分布,其中转换单元含有4路DAC(分辨率可配置为8至10位),采用逐次逼近算法,可利用这些DAC实现高达800KHz采样率的ADC(见图4)。

图4 数据转换模块的框图

数据转换模块包含4个8位的逐次比较寄存器(SAR),它可以和内部的DAC联合工作,以获得模/数转换。

每一个通道有一个独立的SAR,它接收逐次比较的结果,并驱动对应的DAC,每一个通道的转换可以独立进行。当转换模块编程为9或10位ADC转换时,相应的SAR形成组:9位ADC时,SAR1和SAR2为一组,SAR3和SAR4为一组;10位ADC时,所有4个SAR形成一组。这时,成组的SAR各自工作1至2个周期,在转换结束时,SAR将其内容寄存在输入/输出寄存器中,并使能中断产生模块。在连续转换模式下,将启动下一次转换。在转换过程中,可编程逻辑模块可以独立发布转换命令,这将给本次以及下一次转换带来错误。在连续转换模式下,这将导致致命错误,因为错误是可以传递的,并将得到不可预料的结果。

其控制部分是一个标准的8051微处理器。复合后,8051核首先对可编程元胞进行配置,配置完毕后可以当作一个通用的微处理器使用。为了更好的支持FIPSOC的动态可重构特性,已对其指令和功能单元做了一些改进。

CypressPSoC器件

Cypress半导体公司的PSoC混合信号架构将可编程的模拟与数字模块同8位微控制器进行了完美集成,这种独特的功能组合使设计人员能够针对各种应用实现无与伦比的灵活性。最新CY8C23x33器件采用8位逐次逼近ADC,能实现高达375Ksps的采样率。此外,该解决方案还具备可实现出色可配置性的26个GPIO,能够快速适应不断变化的特性要求。该器件采用5x5mm的QFN封装,能够最大限度地缩小板极空间。